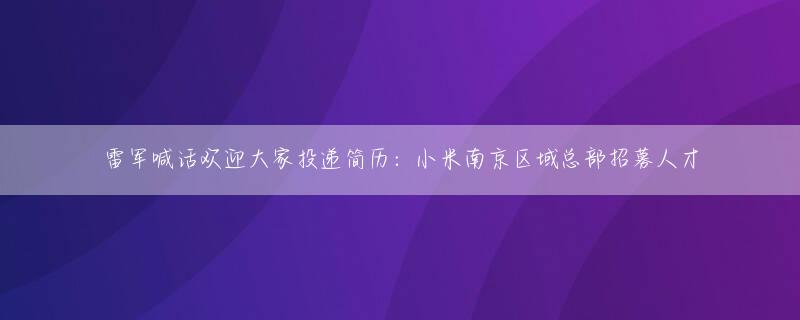

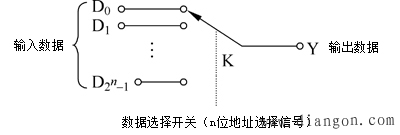

除了前面讲过的编码器、译码器,还有一种经常使用的集成组合逻辑电路器件,就是数据选择器。数据选择器的功能是根据地址选择码从多路输入数据中选择一路送到输出。其作用可用图1所示的单刀多掷开关表示。D0~D2n-1为输入数据,Y为选择输出的数据,S是选择开关,实际上是n位地址信号,最大可以控制选择的数据为2n个。

|

| 图1 数据选择器的功能示意图 |

1、数据选择器的工作原理 |

常用的数据选择器有4选1、8选1、16选1等多种类型。下面以4选1数据选择器为例介绍数据选择器的工作原理。

根据前面介绍的数据选择器的功能,可以列出4选1数据选择器的逻辑功能表,如表5-7-1所示。其中D0~D3为数据输入端,A0、A1为数据选择端。

表5-7-1 4选1数据选择器的逻辑功能表

| 地址输入 | 输出 | |

| A1 | A0 | Y |

| 0 | 0 | D0 |

| 0 | 1 | D1 |

| 1 | 0 | D2 |

| 1 | 1 | D3 |

由逻辑功能表可以写出输出与输入之间的表达式为

| (1) |

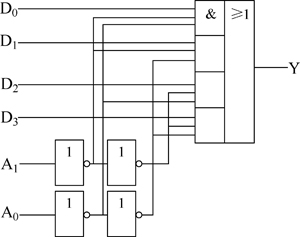

由逻辑表达式画出4选1数据选择器逻辑电路2所示。

|

| 图2 4选1数据选择器的逻辑电路图 |

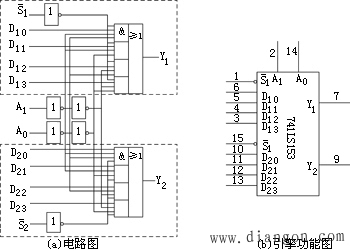

74LS153是一种集成的双4选1数据选择器逻辑器件。图3所示为74LS153的逻辑电路图和框图。

|

| 图3 74LS153双4选1数据选择器 |

由图3(a)可知,74LS153的逻辑电路中包含两个4选1数据选择器,它们的数据输入端分别为D10、D11、D12、D13和D20、D21、D22、D23,数据输出端分别为Y1和Y2。它们有公共的地址选择输入端A0、A1。除此之外,还各自有有一个使能控制端和。由图3(a)可以写出输入与输出之间的逻辑函数式为

| (2) |

由式(2)可以看出,只有当使能控制端=0、=0时,数据选择器才能正常工作,否则数据输出端锁定在低电平。故使能控制端为低电平有效。

74LS153的逻辑功能表如表2所示。

表2 74LS153的逻辑功能表

| 控制端 | 地址输入 | 输出 | |

| A1 | A0 | Y |

| 1 | × | × | 0 |

| 0 | 0 | 0 | D0 |

| 0 | 0 | 1 | D1 |

| 0 | 1 | 0 | D2 |

| 0 | 1 | 1 | D3 |

2、数据选择器的应用

(1)数据选择器的扩展应用

可以用多片少数据输入的数据选择器设计多数据输入的数据选择器。

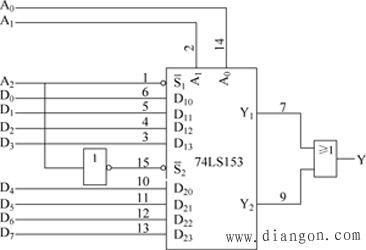

例1:用74LS153设计一个8选1的数据选择器。

解:74LS153是一个双4选1数据选择器。有两个公用的地址选择输入端,8个数据输入端。8选1数据选择器需要3个地址输入端(23=8),因此需要用使能控制端来补充地址输入端的不足。用双4选1数据选择器芯片74LS153设计的8选1数据选择器的电路如图4所示。

|

| 图4 用双4选1数据选择器接成8选1数据选择器的电路图 |

当A2=0时,上边的4选1数据选择器工作,根据地址输入端A0、A1的状态,输出端Y1选择输出D0~D3,此时Y2=0,故Y=Y1;当A2=1时,下边的4选1数据选择器工作,根据地址输入端A0、A1的状态,输出端Y2选择输出D4~D7,此时Y1=0,故Y=Y2。逻辑函数式为

| (3) |

也可以添加使能控制端对所接成的8选1数据选择器的工作状态进行控制。

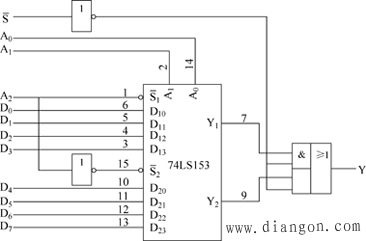

添加使能控制端的8选1数据选择器的电路如图5所示。

|

| 图5 有使能控制端的8选1数据选择器框图 |

由图5可知,当=0 时,8选1数据选择器正常工作;当=1时,8选1数据选择器的输出被锁定在低电平。

(2)用数据选择器设计组合逻辑电路 |

由表2可知,具有两位地址输入A0、A1的4选1数据选择器,当使能控制端=0时,输出与输入之间的逻辑关系式为

| (4) |

若将A0、A1作为两个输入变量,同时令D0~D3为第三个变量的适当状态(包括原变量、反变量、0和1),就可以用4选1数据选择器实现任何形式的三变量组合逻辑函数。

同理,用由n位地址输入端的数据选择器可以实现任何形式的变量数不大于n+1的组合逻辑函数。

例2:用4选1数据选择器实现以下组合逻辑函数:

| (5) |

解:将式(4)化成与式(5)相对应的形式:

| (6) |

将式(6)与式(4)比较可知,只要令数据选择器的数据输入端为

、、、、、

则数据选择器的输出就是所要表达的组合逻辑函数。